だいぶ前に購入したXilinxのFPGAであるZyboですが、いい加減Lチカさせてみたいと思ったのでLチカにいたるメモを残します。

開発環境

Vivado web pack

2015.2

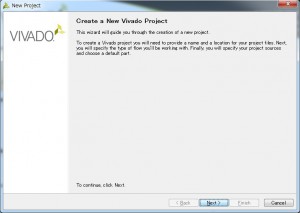

Create New Objectをクリック

Nextをクリック

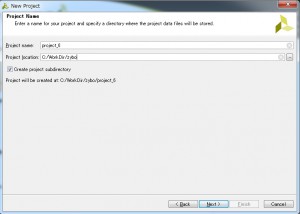

適当にプロジェクト名をいれてNextをクリック

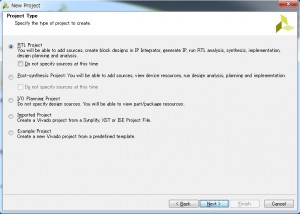

RTL Projectが選ばれていることを確認してNextをクリック

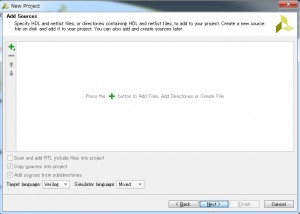

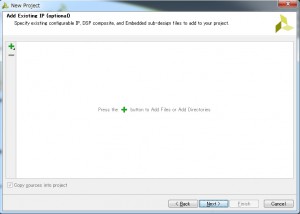

Nextをクリック

Nextをクリック

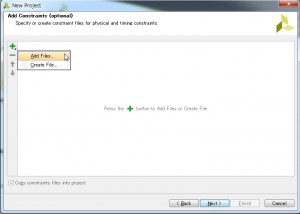

+をクリックしてAdd Fileをクリック

XDCファイルを読み込む必要があるのですが、これはZyboのボードで使用できるピンの情報を定義された物です。

DigilentのサイトからVivado用のファイルをダウンロードしてください。

DSD-0000446と書かれている物です。

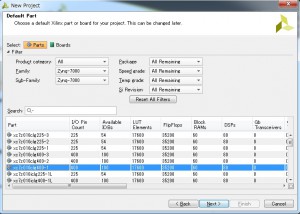

xc7z010clg400-1を選択

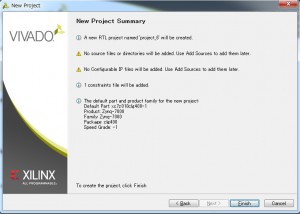

Finishをクリック

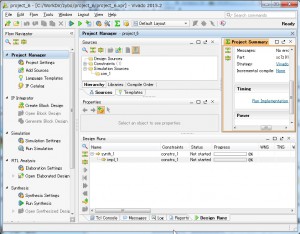

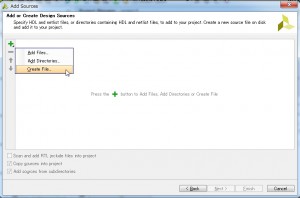

Add Sourcesをクリック

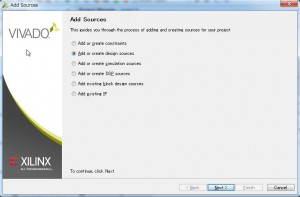

Add or create design sourcesが選択されていることを確認してNext

+をクリックしてCreate File

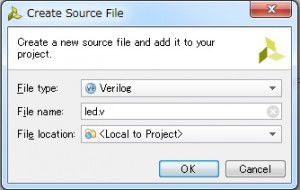

とりあえずled.vとします。言語はVerilogで。

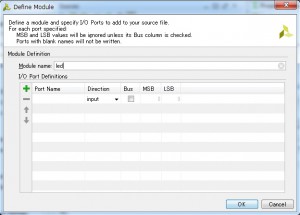

あとでIOポートの設定をするのでOKをクリック

警告が出ますがYesをクリック

led.vがプロジェクトに追加されます。

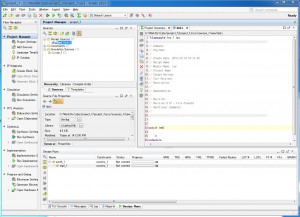

やっとコーディングできる状態になりました。

こんな感じでコードを書きます

module led(

SW

LED

);

input SW;

output LED;

assign LED = ~SW;

endmodule

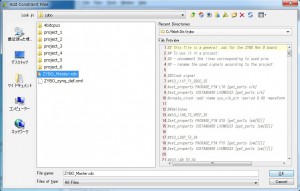

XDCファイルを編集します

こんな感じでコメントはずしてPin名を入れます

##IO_L7P_T1_34

set_property PACKAGE_PIN Y16 [get_ports {SW}]

set_property IOSTANDARD LVCMOS25 [get_ports {SW}]

##IO_L23P_T3_35

set_property PACKAGE_PIN M14 [get_ports {LED}]

set_property IOSTANDARD LVCMOS33 [get_ports {LED}]

とりあえずここまで